# MultiProcessor Specification

Version 1.4

<u>August 1996</u>

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

A license is hereby granted to copy and reproduce this specification for internal use only.

No other license, express or implied, by estoppel or otherwise, to any other intellectual property rights is granted herein.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to implementation of information in this specification. Intel does not warrant or represent that such implementation(s) will not infringe such rights.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\* Third-party trademarks are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Center P.O. Box 7641 Mt. Prospect IL 60056-7641

or call 800-879-4683

Copyright © 1993-1996. Intel Corporation, All Rights Reserved.

## **Revision History**

| Revision    | Revision History Date                                                                                                                                                                                                |                 |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

|             | Pre-release Version 1.0. Formerly called "PC+MP Specification"                                                                                                                                                       | 10/27/93        |  |  |  |  |

| -001        | Version 1.1. Resolves conflicts with MCA-based systems. The following changes have been made:                                                                                                                        | 4/11/94         |  |  |  |  |

|             | 1. Two MP feature information bytes were moved from the BIOS System<br>Configuration Table to the RESERVED area of the MP Floating Pointer<br>Structure.                                                             |                 |  |  |  |  |

|             | 2. If the MP Floating Pointer Structure is present, it indicates that the system is MP-compliant, in accordance with this specification. (Previously, this was indicated by bit 0 of MP Feature Information Byte 1.) |                 |  |  |  |  |

|             | 3. One more hardware default system configuration was added for MCA+PCI with the integrated APIC.                                                                                                                    |                 |  |  |  |  |

| -002        | Minor technical corrections.                                                                                                                                                                                         | 6/1/94          |  |  |  |  |

| -003        | Added Appendix D: Multiple I/O APIC Multiple PCI Bus Systems.                                                                                                                                                        | 9/1/94          |  |  |  |  |

| <u>-004</u> | Version 1.4. Added extended configuration table to improve support for<br>multiple PCI bus configurations and improve future expandability. Made<br>clarifications to Appendix B.                                    | <u>7/1/95</u>   |  |  |  |  |

| <u>-005</u> | Added Appendix E: Errata. Includes information for hierarchical PCI bus.                                                                                                                                             | <u>08/15/96</u> |  |  |  |  |

## **Table of Contents**

### Chapter 1 Introduction

| 1.1 | Goals                             | 1-1 |

|-----|-----------------------------------|-----|

| 1.2 | Features of the Specification     | 1-2 |

| 1.3 | Scope                             | 1-2 |

| 1.4 | Target Audience                   | 1-3 |

| 1.5 | Organization of This Document     | 1-3 |

| 1.6 | Conventions Used in This Document | 1-4 |

| 1.7 | For More Information              | 1-4 |

### Chapter 2 System Overview

| Hardwa  | are Overview                               | 2-2                                  |

|---------|--------------------------------------------|--------------------------------------|

| 2.1.1   | System Processors                          | 2-2                                  |

| 2.1.2   | Advanced Programmable Interrupt Controller | 2-3                                  |

| 2.1.3   | System Memory                              | 2-4                                  |

| 2.1.4   | I/O Expansion Bus                          | 2-4                                  |

| BIOS C  | Dverview                                   | 2-5                                  |

| Operati | ing System Overview                        | 2-5                                  |

|         | 2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>BIOS C | <ul> <li>Hardware Overview</li></ul> |

### Chapter 3 Hardware Specification

| 3.1 | Systen  | n Memory Configuration                                 | 3-1  |

|-----|---------|--------------------------------------------------------|------|

| 3.2 | Systen  | n Memory Cacheability and Shareability                 | 3-2  |

| 3.3 | Extern  | al Cache Subsystem                                     | 3-4  |

| 3.4 | Lockin  | g                                                      | 3-4  |

| 3.5 | Postec  | I Memory Write                                         | 3-5  |

| 3.6 | Multipr | ocessor Interrupt Control                              | 3-5  |

|     | 3.6.1   | APIC Architecture                                      | 3-5  |

|     | 3.6.2   | Interrupt Modes                                        | 3-6  |

|     |         | 3.6.2.1 PIC Mode                                       | 3-7  |

|     |         | 3.6.2.2 Virtual Wire Mode                              | 3-9  |

|     |         | 3.6.2.3 Symmetric I/O Mode                             | 3-11 |

|     | 3.6.3   | Assignment of System Interrupts to the APIC Local Unit | 3-12 |

|     | 3.6.4   | Floating Point Exception Interrupt                     | 3-12 |

|     | 3.6.5   | APIC Memory Mapping                                    | 3-12 |

|     |         |                                                        |      |

#### Contents

# intel

|           | 3.6.6    | APIC Identification                                  |

|-----------|----------|------------------------------------------------------|

|           | 3.6.7    | APIC Interval Timers                                 |

|           | 3.6.8    | Multiple I/O APIC Configurations                     |

| 3.7       | RESET    | Support3-14                                          |

|           | 3.7.1    | System-wide RESET                                    |

|           | 3.7.2    | System-wide INIT                                     |

|           | 3.7.3    | Processor-specific INIT                              |

| 3.8       | System   | Initial State3-16                                    |

| 3.9       | Support  | t for Fault-resilient Booting3-16                    |

| Chapter 4 | MP Co    | onfiguration Table                                   |

| 4.1       | MP Floa  | ating Pointer Structure4-3                           |

| 4.2       | MP Cor   | nfiguration Table Header4-5                          |

| 4.3       | Base M   | P Configuration Table Entries4-6                     |

|           | 4.3.1    | Processor Entries4-7                                 |

|           | 4.3.2    | Bus Entries4-10                                      |

|           | 4.3.3    | I/O APIC Entries4-12                                 |

|           | 4.3.4    | I/O Interrupt Assignment Entries4-12                 |

|           | 4.3.5    | Local Interrupt Assignment Entries4-15               |

| 4.4       | Extende  | ed MP Configuration Table Entries4-17                |

|           | 4.4.1    | System Address Space Mapping Entries4-18             |

|           | 4.4.2    | Bus Hierarchy Descriptor Entries4-21                 |

|           | 4.4.3    | Compatibility Bus Address Space Modifier Entries4-22 |

| Chapter 5 | Defaul   | It Configurations                                    |

| 5.1       | Discrete | e APIC Configurations5-2                             |

| 5.2       | Integrat | ed APIC Configurations5-4                            |

| 5.3       | Assignr  | nent Of I/O Interrupts To The APIC I/O Unit5-6       |

|           | 5.3.1    | EISA and IRQ135-7                                    |

|           | 5.3.2    | Level-triggered Interrupt Support5-7                 |

| 5.4 | Assignment Of System Inte | rrunto To The Ar |               | 57 |

|-----|---------------------------|------------------|---------------|----|

| 5.4 | Assignment Of System Inte | nupis to the Ar  | TO LOCAL OTHL |    |

### Appendix A System BIOS Programming Guidelines

| A.1    | В     | BIOS Post Initialization A-1                    |     |  |

|--------|-------|-------------------------------------------------|-----|--|

| A.2    | 2 C   | Controlling the Application Processors          |     |  |

| A.3    | 6 P   | Programming the APIC for Virtual Wire Mode      | A-2 |  |

| A.4    | . C   | Constructing the MP Configuration Table         | A-4 |  |

| Append | dix B | Operating System Programming Guidelines         |     |  |

| B.1    | 0     | Dperating System Boot-up                        | B-1 |  |

| B.2    | 2 O   | Dperating System Booting and Self-configuration | B-2 |  |

| B.3    | ln    | nterrupt Mode Initialization and Handling       | B-2 |  |

| B.4    | - A   | Application Processor Startup                   | B-3 |  |

|        | B     | 3.4.1 USING INIT IPI                            | B-4 |  |

|        | B     | 3.4.2 USING STARTUP IPI                         | B-5 |  |

| B.5    | A     | AP Shutdown Handling                            | B-5 |  |

| B.6    | 6 O   | Other IPI Applications                          | B-6 |  |

|        | B     | 3.6.1 Handling Cache Flush                      | B-6 |  |

|        | B     | 3.6.2 Handling TLB Invalidation                 | B-6 |  |

|        | B     | 3.6.3 Handling PTE Invalidation                 | B-6 |  |

| B.7    | S S   | Spurious APIC Interrupts                        | B-6 |  |

| B.8    | s S   | Supporting Unequal Processors                   | B-7 |  |

|        |       |                                                 |     |  |

### Appendix C System Compliance Checklist

#### Appendix D Multiple I/O APIC Multiple PCI Bus Systems

| D.1 | Interrupt Routing with Multiple APICs             | D-1 |

|-----|---------------------------------------------------|-----|

|     | D.1.1 Variable Interrupt Routing                  |     |

|     | D.1.2 Fixed Interrupt Routing                     | D-2 |

| D.2 | Bus Entries in Systems with More Than One PCI Bus | D-3 |

| D.3 | I/O Interrupt Assignment Entries for PCI Devices  | D-3 |

|     |                                                   |     |

#### Appendix E Errata

Glossary

#### Contents

# intel

### Figures

| 1-1.  | Conceptual Overview                                     | 1-1  |

|-------|---------------------------------------------------------|------|

| 1-2.  | Memory Layout Conventions                               | 1-4  |

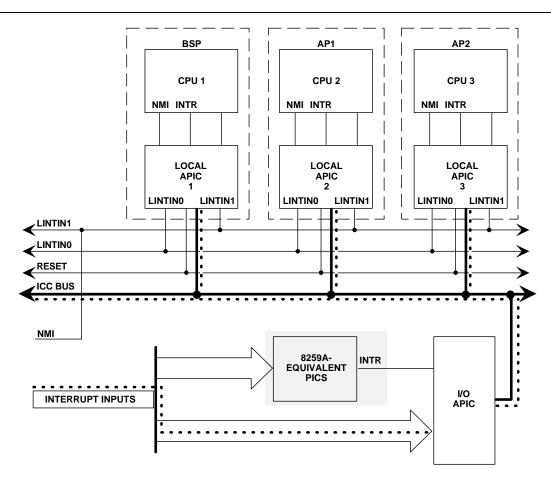

| 2-1.  | Multiprocessor System Architecture                      | 2-2  |

| 2-2.  | APIC Configuration                                      | 2-3  |

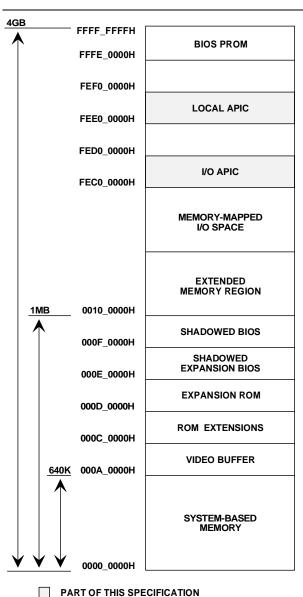

| 3-1.  | System Memory Address Map                               | 3-2  |

| 3-2.  | PIC Mode                                                | 3-8  |

| 3-3.  | Virtual Wire Mode via Local APIC                        | 3-9  |

| 3-4.  | Virtual Wire Mode via I/O APIC                          | 3-10 |

| 3-5.  | Symmetric I/O Mode                                      | 3-11 |

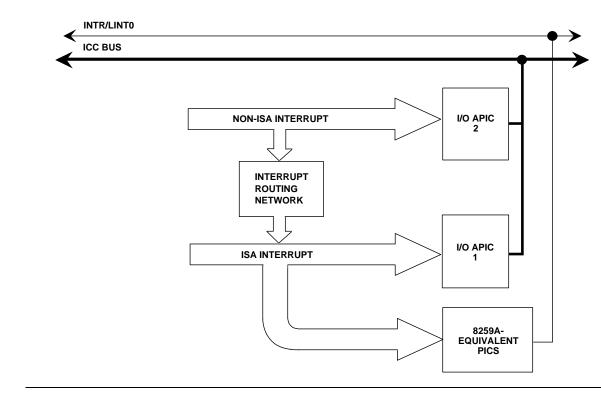

| 3-6.  | Multiple I/O APIC Configurations                        | 3-14 |

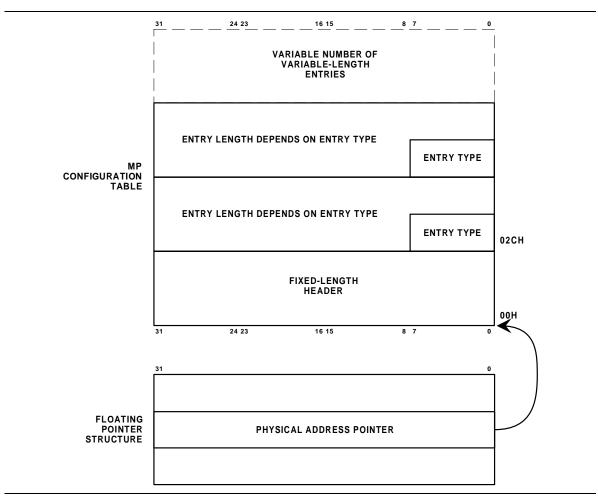

| 4-1.  | MP Configuration Data Structures                        | 4-1  |

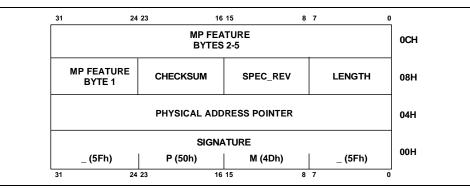

| 4-2.  | MP Floating Pointer Structure                           | 4-3  |

| 4-3.  | MP Configuration Table Header                           | 4-5  |

| 4-4.  | Processor Entry                                         | 4-7  |

| 4-5.  | Bus Entry                                               | 4-10 |

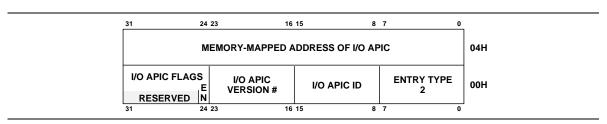

| 4-6.  | I/O APIC Entry                                          | 4-12 |

| 4-7.  | I/O Interrupt Entry                                     | 4-13 |

| 4-8.  | Local Interrupt Entry                                   | 4-15 |

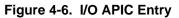

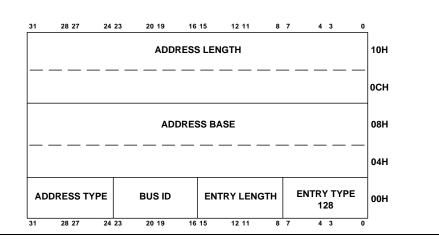

| 4-9.  | System Address Space Entry                              | 4-18 |

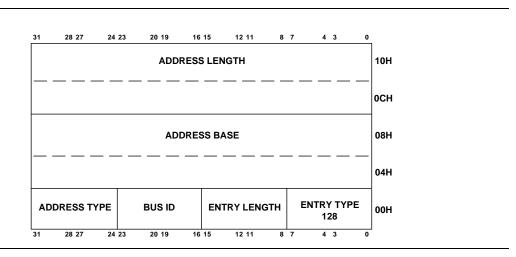

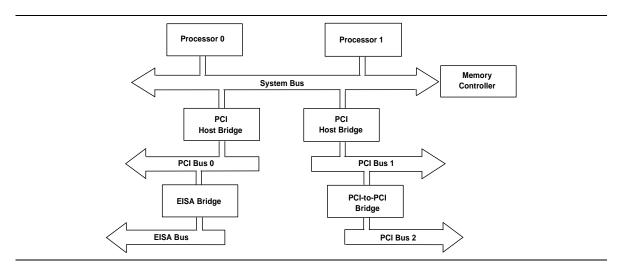

| 4-10. | Example System with Multiple Bus Types and Bridge Types | 4-19 |

| 4-11. | Bus Hierarchy Descriptor Entry                          | 4-21 |

| 4-12. | Compatibility Bus Address Space Modifier Entry          | 4-23 |

| 5-1.  | Default Configuration for Discrete APIC                 | 5-3  |

| 5-2.  | Default Configuration for Integrated APIC               | 5-5  |

|       |                                                         |      |

|       |                                                         |      |

### Tables

| 1-1. | Document Organization                                               | 1-3 |

|------|---------------------------------------------------------------------|-----|

| 3-1. | Memory Cacheability Map                                             | 3-3 |

| 3-2. | APIC Versions                                                       | 3-6 |

| 4-1. | MP Floating Pointer Structure Fields                                | 4-3 |

| 4-2. | MP Configuration Table Header Fields                                | 4-6 |

| 4-3. | Base MP Configuration Table Entry Types                             | 4-7 |

| 4-4. | Processor Entry Fields                                              | 4-8 |

| 4-5. | Intel486 <sup>™</sup> and Pentium <sup>®</sup> Processor Signatures | 4-9 |

#### Contents

# intel

|          | 4-6.  | Feature Flags from CPUID Instruction4-9                     |

|----------|-------|-------------------------------------------------------------|

|          | 4-7.  | Bus Entry Fields4-10                                        |

|          | 4-8.  | Bus Type String Values4-11                                  |

|          | 4-9.  | I/O APIC Entry Fields4-12                                   |

|          | 4-10. | I/O Interrupt Entry Fields4-14                              |

|          | 4-11. | Interrupt Type Values4-15                                   |

|          | 4-12. | Local Interrupt Entry Fields                                |

|          | 4-13. | Extended MP Configuration Table Entry Types4-17             |

|          | 4-14. | System Address Space Mapping Entry Fields4-19               |

|          | 4-15. | Bus Hierarchy Descriptor Entry Fields4-22                   |

|          | 4-16. | Compatibility Bus Address Space Modifier Entry Fields4-24   |

|          | 4-17. | Predefined Range Lists4-24                                  |

|          | 5-1.  | Default Configurations5-2                                   |

|          | 5-2.  | Default Configuration Interrupt Assignments5-6              |

|          | 5-3.  | Assignment of System Interrupts to APIC Local Unit5-7       |

|          | D-1.  | I/O Interrupt Entry Source Bus IRQ Field for PCI DevicesD-3 |

| Examples |       |                                                             |

|          | A 4   | Dreamanning Least ADIO for Virtual Wire Made                |

| A-1. | Programming Local APIC for Virtual Wire Mode A- |

|------|-------------------------------------------------|

| B-1. | Universal Start-up AlgorithmB-3                 |

## 1 Introduction

The MultiProcessor Specification, hereafter known as the "MP specification," defines an enhancement to the standard to which PC manufacturers design DOS-compatible systems. MP-capable operating systems will be able to run without special customization on multiprocessor systems that comply with this specification. End users who purchase a compliant multiprocessor system will be able to run their choice of operating systems.

The MP specification covers PC/AT-compatible MP platform designs based on Intel processor architectures and Advanced Programmable Interrupt Controller (APIC) architectures. The term "PC/AT-compatible" here refers to the software-visible components of the PC/AT, not to hardware features, such as the bus implementation, that are not visible to software. An implementation of this specification may incorporate one or more industry standard buses, such as ISA, EISA, MCA, PCI, or other OEM-specific buses.

#### 1.1 Goals

The intent of this specification is to establish an MP Platform interface standard that extends the performance of the existing PC/AT platform beyond the traditional single processor limit, while maintaining 100% PC/AT binary compatibility.

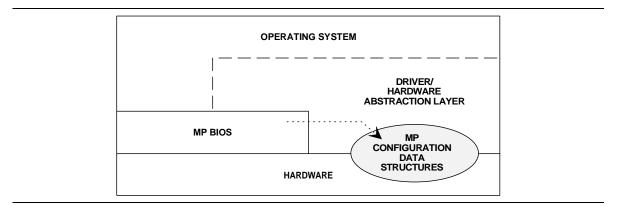

The ultimate goal is to enable scalable, high-end workstations and enterprise server systems that provide computer users with superior price/performance and have the ability to execute all existing AT binaries, as well as MP-ready software packages on shrink-wrapped MP operating systems. Figure 1-1 shows that at the heart of the specification are the data structures that define the configuration of the MP system. The BIOS constructs the MP configuration data structures, presenting the hardware in a known format to the standard device drivers or to the hardware abstraction layer of the operating system. The specification details default hardware configurations, and, for added flexibility, outlines extensions to the standard BIOS.

Figure 1-1. Conceptual Overview

#### **1.2 Features of the Specification**

The MP specification includes the following features:

- A multiprocessor extension to the PC/AT platform that runs all existing uniprocessor shrink-wrapped binaries, as well as MP binaries.

- Support for symmetric multiprocessing with one or more processors that are Intel architecture instruction set compatible, such as the CPUs in the Intel486<sup>TM</sup> and the Pentium<sup>®</sup> processor family.

- Support for symmetric I/O interrupt handling with the APIC, a multiprocessor interrupt controller.

- Flexibility to use a BIOS with minimal MP-specific support.

- An optional MP configuration table to communicate configuration information to an MP operating system.

- Incorporation of ISA and other industry standard buses, such as EISA, MCA, VL and PCI buses in MP-compliant systems.

- Requirements that make secondary cache and memory bus implementation transparent to software.

#### 1.3 Scope

There are many vendors building innovative MP systems based on Intel architectures today. Intel supports and encourages vendors to develop advanced approaches to the technological requirements of today's computing environments. In no way does the MP specification prevent system manufacturers from adding their own unique value to MP systems. This specification does not define the only way that multiprocessor systems can be implemented. Vendors may, for example, create noncompliant, high-performance, scalable multiprocessor systems that do not have the PC/AT compatibility required by this specification. Hardware vendors will always have the option of offering one or more customized operating systems that support the unique, value-added capabilities that they have designed into their systems. End users will be able to benefit from the additional capabilities that these vendors offer.

The MP specification benefits PC vendors who wish to offer MP-enabled systems without having to invest in the customization of one or more operating systems. This specification focuses on providing a standard mechanism to add MP support to personal computers built around the PC/AT hardware standard. With that goal, the specification covers only the minimum set of capabilities required to extend the PC/AT platform to be MP-capable. The hardware required to implement the MP specification is kept to a minimum, as follows:

- One or more processors that are Intel architecture instruction set compatible, such as the CPUs in the Intel486 or Pentium processor family.

- One or more APICs, such as the Intel 82489DX Advanced Programmable Interrupt Controller or the integrated APIC, such as that on the Intel Pentium 735\90 and 815\100 processors, together with a discrete I/O APIC unit.

- The necessary supporting electronics to duplicate the initialization and signaling protocol described in this specification.

- PC/AT-compliant hardware.

In addition to the hardware requirements, this document also specifies MP features that are visible to the BIOS and operating system. However, it is important to understand that as hardware technology progresses, the functions performed by the BIOS may change in accordance with the hardware technology. **ONLY THE INTERFACE TO THE OPERATING SYSTEM LEVEL IS EXPECTED TO REMAIN CONSTANT.**

This specification does not address issues relating to the processor's System Management Mode (SMM).

### 1.4 Target Audience

This document is intended for the following users:

- OEMs who will be creating PC/AT-compatible, MP-ready hardware based on this specification.

- BIOS developers, either those who create general-purpose BIOS products or those who modify these products to suit specific MP hardware.

- Operating-system developers who will be adapting MP operating systems to run on the class of MP-ready platform specified here.

### 1.5 Organization of This Document

Table 1-1 shows the organization of this document.

|                   | -                                                              |  |  |

|-------------------|----------------------------------------------------------------|--|--|

| Chapter           | Description                                                    |  |  |

| 2                 | Overview of the MultiProcessor Specification                   |  |  |

| 3                 | Specification of the MP hardware                               |  |  |

| 4                 | Specification of MP configuration information available to OS  |  |  |

| 5                 | Specification of default hardware configurations               |  |  |

| Appendix A        | Guidelines for MP BIOS programming                             |  |  |

| Appendix B        | Guidelines for MP operating system programming                 |  |  |

| Appendix C        | Checklist for hardware compliance to the specification         |  |  |

| <u>Appendix D</u> | Clarifications for multiple I/O APIC, multiple PCI bus systems |  |  |

| Glossary          | Definitions of specialized terms used in this document         |  |  |

| Table 1-1. Document Organizat |

|-------------------------------|

|-------------------------------|

Signal names that are followed by the character # represent active low signals. For example, FERR# is active when at its low-voltage state.

Throughout this document, the Intel 82489DX APIC is referred to as the "discrete APIC." The term "integrated APIC" is used to refer to an APIC integrated with other system components, such as the Pentium 735\90 and 815\100 processors. This specification uses the term APIC to refer to both discrete and integrated versions.

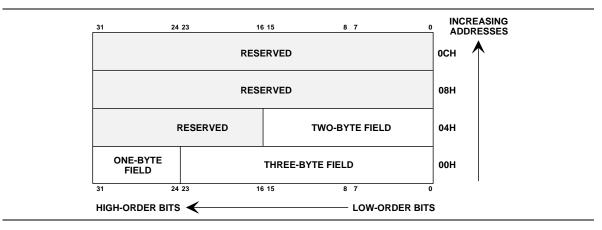

The processors of the Intel486 and Pentium processor family are "little endian" machines. This means that the low-order byte of a multibyte data item in memory is at the lowest address, while the high-order byte is at the highest address. Illustrations of data structures in memory show the lowest addresses at the bottom and the highest addresses at the top of the illustration, as shown in Figure 1-2. Bit positions are numbered from right to left.

Figure 1-2. Memory Layout Conventions

In some memory layout descriptions, certain fields are marked **RESERVED**. Software should initialize these fields as binary zeros, but should otherwise treat them as having a future, though unknown effect. SOFTWARE SHOULD AVOID ANY DEPENDENCE ON THE VALUES IN THE RESERVED FIELDS.

#### **1.7 For More Information**

For more information, refer to any of the following documents:

- 82489DX Advanced Programmable Interrupt Controller (data book), Intel order number 290446

- Intel486 Microprocessor Programmer's Reference Manual, Intel order number 240486

- Intel Processor Identification with the CPUID Instruction AP-485, Intel order number 241618

- Pentium Processor User's Manual, Intel order number 241428

## 2 System Overview

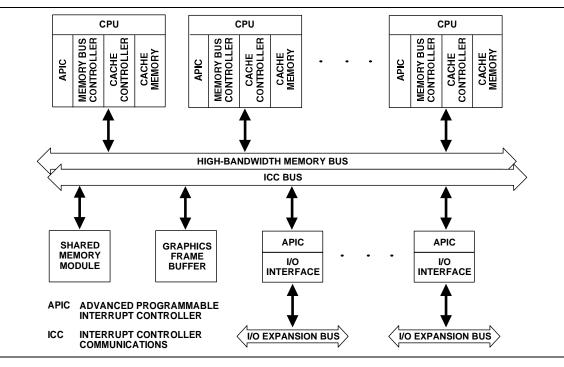

In the realm of multiprocessor architectures, there are several conceptual models for tying together computing elements, and there are a variety of interconnection schemes and details of implementation. Figure 2-1 shows the general structure of a design based on the MP specification. The MP specification's model of multiprocessor systems incorporates a tightly-coupled, shared-memory architecture with a distributed interprocessor and I/O interrupt capability. It is fully symmetric; that is, all processors are functionally identical and of equal status, and each processor can communicate with every other processor. There is no hierarchy, no master-slave relationship, no geometry that limits communication only to "neighboring" processors. The model is symmetric in two important respects:

- *Memory symmetry*. Memory is symmetric when all processors share the same memory space and access that space by the same addresses. Memory symmetry offers a very important feature—the ability for all processors to execute a single copy of the operating system. Any existing system and application software will execute the same, regardless of the number of processors installed in a system.

- *I/O symmetry*. I/O is symmetric when all processors share access to the same I/O subsystem (including I/O ports and interrupt controllers) and any processor can receive interrupts from any source. Some multiprocessor systems that have symmetric access to memory are actually asymmetric with regard to I/O interrupts, because they dedicate one processor to interrupt functions. I/O symmetry helps eliminate the potential of an I/O bottleneck, thereby increasing system scalability.

With both memory and I/O symmetry, a system that complies with the MP specification can achieve hardware scalability as well as support software standardization. Based on this kind of scalable architecture, systems developers can produce systems that span a wide range of price and performance, and that all execute the same binaries.

In'

Figure 2-1. Multiprocessor System Architecture

#### 2.1 Hardware Overview

The MP specification defines a system architecture based on the following hardware components:

- One or more processors that are Intel architecture instruction set compatible, such as the CPUs in the Intel486 and the Pentium processor family.

- One or more APICs, such as the Intel 82489DX Advanced Programmable Interrupt Controller or the integrated APIC on the Pentium 735\90 and 815\100 processors.

- Software-transparent cache and shared memory subsystem.

- Software-visible components of the PC/AT platform.

#### 2.1.1 System Processors

To maintain compatibility with existing PC/AT software products, this specification is based on the Intel486 and the Pentium processor family. To achieve a minimum level of MP system performance, two or more processors that are Intel architecture instruction set compatible are required.

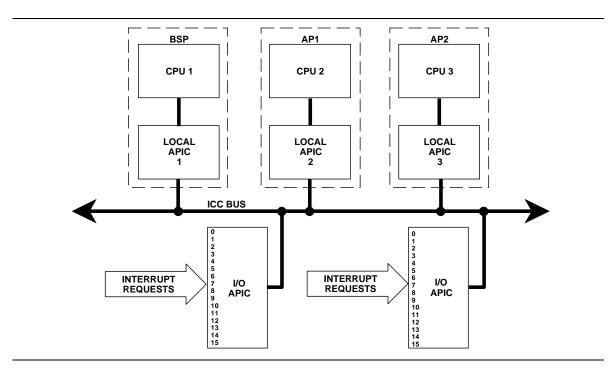

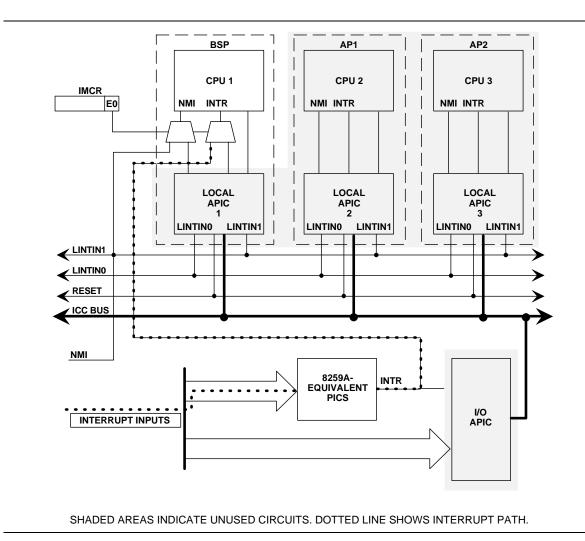

Figure 2-2 gives a different point of view of a compliant system, showing the configuration of the APICs with respect to the CPUs. While all processors in a compliant system are functionally identical, this specification classifies them into two types: the bootstrap processor (BSP) and the application processors (AP). Which processor is the BSP is determined by the hardware or by the hardware in conjunction with the BIOS. This differentiation is for convenience and is in effect

only during the initialization and shutdown processes. The BSP is responsible for initializing the system and for booting the operating system; APs are activated only after the operating system is up and running. CPU1 is designated as the BSP. CPU2, CPU3, and so on, are designated as the APs.

Figure 2-2. APIC Configuration

#### 2.1.2 Advanced Programmable Interrupt Controller

The Advanced Programmable Interrupt Controller (APIC) is based on a distributed architecture in which interrupt control functions are distributed between two basic functional units, the local unit and the I/O unit. The local and I/O units communicate through a bus called the Interrupt Controller Communications (ICC) bus, as shown in Figure 2-2.

In a multiprocessor system, multiple local and I/O APIC units operate together as a single entity, communicating with one another over the ICC bus. The APIC units are collectively responsible for delivering interrupts from interrupt sources to interrupt destinations throughout the multiprocessor system.

The APICs help achieve the goal of scalability by doing the following:

- Off-loading interrupt-related traffic from the memory bus, making the memory bus more available for processor use.

- Helping processors share the interrupt processing load with other processors.

The APICs help achieve the goal of AT-compatibility by cooperating with 8259A-equivalent PICs in the system.

The local APIC units also provide interprocessor interrupts (IPIs), which allow any processor to interrupt any other processor or set of processors. There are several types of IPIs. Among them, the INIT IPI and the STARTUP IPI are specifically designed for system startup and shutdown.

Each local APIC has a Local Unit ID Register and each I/O APIC has an I/O Unit ID Register. The ID serves as a physical name for each APIC unit. It is used by software to specify destination information for I/O interrupts and interprocessor interrupts, and is also used internally for accessing the ICC bus.

Due to the distributed architecture, the APIC local and I/O units can be implemented in either a single chip, such as Intel's 82489DX interrupt controller, or they can be integrated with other parts of the system's components. For example, the local APIC may be integrated with the CPU chip, such as Intel's Pentium processors (735\90, 815\100), and the I/O APIC may be integrated with the I/O chipset, such as Intel's 82430 PCI-EISA bridge chipset.

#### 2.1.3 System Memory

A system that complies with the MP specification uses the standard AT memory architecture. All memory is allocated for system memory with the exception of addresses 0A\_0000h through 0F\_FFFh and 0FFFE\_0000h through 0FFFF\_FFFh, which are reserved for I/O devices and the BIOS.

Compared to a uniprocessor system, a symmetric multiprocessor system imposes a high demand for memory bus bandwidth. The demand is proportional to the number of processors on the memory bus. To reduce memory bus bandwidth limitations, an implementation of this specification should use a secondary cache that has high-performance features, such as a write-back update policy and a snooping cache-consistency protocol. A secondary cache can push the scalability limit upward by reducing bus traffic and increasing bus bandwidth.

While both secondary caches and memory bus controllers are critical components for high performance in a symmetric multiprocessor system, this specification does not detail their implementation, requiring only that they be totally software transparent.

#### 2.1.4 I/O Expansion Bus

The MP specification provides a multiprocessor extension to the industry-standard PC/AT platform. The term "industry-standard PC/AT platform" here refers to the software-visible components of the PC/AT. The standard does not designate a specific bus architecture. All industry-standard buses, such as ISA, EISA, MCA, VL, and PCI, can be incorporated in the design. Systems developers can implement one or more bus types in their designs, depending on the systems' I/O performance or capacity requirements.

#### System Overview

# intel

### 2.2 BIOS Overview

A BIOS functions as an insulator between the hardware on one hand, and the operating system and applications software on the other. A standard uniprocessor BIOS performs the following functions:

- Tests system components.

- Builds configuration tables to be used by the operating system.

- Initializes the processor and the rest of the system to a known state.

- Provides run-time device-oriented services.

For a multiprocessor system, the BIOS may perform the following additional functions:

- Pass configuration information to the operating system that identifies all processors and other multiprocessing components of the system.

- Initialize all processors and the rest of the multiprocessing components to a known state.

This specification allows a wide range of capability in the BIOS. At the minimal end of the capability scale, the system developer can simply insert an MP floating pointer structure in the standard BIOS. The cost of this level of simplicity in the BIOS, however, is that the system developer has less flexibility in the design of the hardware. At the maximal end of the BIOS capability scale might be a BIOS that dynamically configures the system to provide resilience in the face of component malfunctions.

BIOS developers should read Chapters 3, 4, 5, and Appendix A to understand the tradeoffs between hardware and BIOS capabilities.

### 2.3 Operating System Overview

Enabling the creation of shrink-wrapped MP operating systems is one of the principal goals of this specification. This goal is achieved by allowing a flexible balance between the capabilities of the hardware and those of the BIOS. The potentially vast variety of hardware configurations is reduced by the BIOS to a few simple scenarios that can be readily handled by the low-level boot-up phase of the operating system.

Operating-system developers should read Chapters 3, 4, and 5, and Appendixes A and B to fully understand the interface between the BIOS and the operating system.

## 3 Hardware Specification

This section outlines the minimal set of common hardware features necessary for the operating system to operate on multiple hardware platforms. The MP hardware specification defines how the components mentioned in Chapter 2 are implemented. Compliance to the specification involves the following aspects of hardware implementation:

- System memory configuration

- System memory cacheability and shareability

- External cache implementation requirements

- Control of memory contention (locking)

- Ordering of posted memory writes

- Multiprocessor interrupt control

- Reset support

- Interval timer usage

- Support for fault-resilient booting

While the bulk of the MP hardware specification pertains to multiprocessor interrupt control, other areas also require some attention. The following sections take up each of these topics in turn.

#### 3.1 System Memory Configuration

The MP memory specifications are based on the standard PC/AT memory map, which currently has a physical memory space of four gigabytes, as shown in see Figure 3-1. Physical memory should begin at 0 and be contiguous. Memory-mapped I/O devices should be mapped at the top of physical memory. The APIC default base memory addresses defined by this specification are 0FEC0\_0000h and 0FEE0\_0000h.

UNSHADED ADDRESS REGIONS ARE FOR REFERENCE ONLY AND SHOULD NOT BE CONSTRUED AS THE SOLE DEFINITION OF A PC/AT-COMPATIBLE ADDRESS SPACE.

Figure 3-1. System Memory Address Map

#### 3.2 System Memory Cacheability and Shareability

The cacheability and shareability of the physical memory space are defined in Table 3-1. The address space reserved for the local APIC is used by each processor to access its own local APIC. The address space reserved for the I/O APIC must be shareable by all processors to permit dynamic reconfiguration.

| Addresses<br>(in hex)                     | Size  | Description                                | Shared by All<br>Processors? | Cacheable?       | Comment                                                                |  |

|-------------------------------------------|-------|--------------------------------------------|------------------------------|------------------|------------------------------------------------------------------------|--|

| 0000_0000h –<br>0009_FFFFh                | 640KB | Main memory                                | Yes                          | Yes              |                                                                        |  |

| 000A_0000h –<br>000B_FFFFh                | 128KB | Display buffer for<br>video adapters       | Yes                          | No               |                                                                        |  |

| 000C_0000h –<br>000D_FFFFh                | 128KB | ROM BIOS for add-on cards                  | Yes                          | Yes              |                                                                        |  |

| 000E_0000h –<br>000F_FFFFh                | 128KB | System ROM BIOS                            | Yes                          | Yes              |                                                                        |  |

| 0010_0000h –<br>0FEBF_FFFFh               |       | Main memory                                | Yes                          | Yes              | Maximum address<br>depends on total memory<br>installed in the system. |  |

| Not specified.                            |       | Memory-mapped I/O<br>devices               | Yes <sup>2</sup>             | Not<br>specified | Top unused memory                                                      |  |

| 0FEC0_0000h –<br>0FECF_FFFFh <sup>1</sup> |       | APIC I/O unit                              | Yes                          | No               | Refer to the register<br>description in the APIC<br>data book.         |  |

| 0FED0_0000h –<br>0FEDF_FFFFh              |       | Reserved for memory-<br>mapped I/O devices | Yes <sup>2</sup>             | Not<br>specified |                                                                        |  |

| 0FEE0_0000h-<br>0FEEF_FFFFh <sup>1</sup>  |       | APIC Local Unit                            | No                           | No               | Refer to the register<br>description in the APIC<br>data book.         |  |

| 0FEF0_0000h –<br>0FFFD_FFFFh              |       | Reserved for memory-<br>mapped I/O devices | Yes <sup>2</sup>             | Not<br>specified |                                                                        |  |

| 0FFFE_0000h –<br>0FFFF_FFFh               | 128KB | Initialization ROM                         | Yes                          | Not<br>specified |                                                                        |  |

#### Table 3-1. Memory Cacheability Map

#### NOTES:

1. These addresses are part of this specification. The other address regions in this table are shown for reference only, and should not be construed as the sole definition of a PC/AT-compatible address space format or cache.

2. Any memory-mapped device should be shareable unless the nature of the device is that there is one device per processor.

### 3.3 External Cache Subsystem

Intel-compatible processors support multiprocessing both on the processor bus and on a memory bus, both with and without secondary cache units. Due to the high bandwidth demands of multiprocessor systems, external caches are often employed to improve performance. The existence and implementation details of external caches are not a part of this specification. However, when external caches are used, they must conform to certain requirements with regard to the following design issues:

- *Maintaining cache coherency*—When one processor accesses data cached in another processor's cache, it must not receive incorrect data. If it modifies data, all other processors that access that data also must not receive stale data. External caches must maintain coherency among themselves, and with the main memory, internal caches, and other bus master DMA devices.

- *Cache flushing*—The processor can generate special flush and write-back bus cycles that must be used by external caches in a manner that maintains cache coherency. The actual responses are implementation-specific and may vary from design to design. A program can initiate hardware cache flushing by executing a WBINVD instruction. This instruction is only guaranteed to flush the caches of the local processor. See Appendix B for system-wide flushing mechanisms. Given that cache coherency is maintained by hardware, there is no need for software to issue cache flush instructions under normal circumstances.

- *Reliable communication*—All processors must be able to communicate with each other in a way that eliminates interference when more than one processor accesses the same area in memory simultaneously. The processor uses the LOCK# signal for this purpose. External caches must ensure that all locked operations are visible to other processors.

- *Write ordering*—In some circumstances, it is important that memory writes be observed externally in precisely the same order as programmed. External write buffers must maintain the write ordering of the processor.

### 3.4 Locking

To protect the integrity of certain critical memory operations, Intel-compatible processors provide an output signal called LOCK#. For any given memory access, LOCK# is asserted once, but may remain asserted for as many memory bus cycles as required to complete the memory operation. It is the responsibility of the system hardware designers to use this signal to control memory accesses among processors.

A compliant system in multiprocessor mode must guarantee atomicity of locked-aligned memory operations; however, the implementation is not specified in this specification. A compliant system must lock at least the area of memory defined by the destination operand. A specific implementation may lock a broader area—it may even lock the entire bus. Therefore, software must consider this behavior.

To guarantee AT compatibility, locking of misaligned memory operations over other ATcompatible buses in the compliant system must be strictly implemented in accordance with the bus specifications. A compliant system may not be required to support the misaligned memory operations over its internal shared memory bus, if it is AT compatible. Operating system and

software developers must <u>ensure</u> that data is aligned <u>if locked access is required</u>, because <u>lock</u> <u>operations on</u> misaligned data <u>are</u> not guaranteed to work <u>on all platforms</u>.

#### 3.5 Posted Memory Write

When controlling I/O devices, it is important that memory and I/O operations be carried out in the order programmed. Intel-compatible processors do not buffer I/O writes; thus, strict ordering among I/O operations is enforced by the processors.

To optimize memory performance, processors and chipsets often implement write buffers and writeback caches. Intel-compatible processors guarantee processor ordering on all internal cache and write buffer accesses. However, chipsets must also guarantee processor ordering on all external memory accesses.

For systems based on the integrated APIC, posting of memory writes may result in spurious interrupts for memory-mapped I/O devices using level-triggered interrupts. I/O device drivers must serialize instructions to ensure that the device interrupt clear command reaches the device before the EOI command reaches the APIC and handles the spurious interrupt in case one occurs.

### 3.6 Multiprocessor Interrupt Control

In an MP-compliant system, interrupts are controlled through the APIC. The following sections describe the APIC architecture and the three interrupt modes allowed in an MP-compliant system.

#### 3.6.1 APIC Architecture

The Intel Advanced Programmable Interrupt Controller (APIC) is based on a distributed architecture. Interrupt control functions are distributed between two basic functional units: the local unit and the I/O unit. The local and I/O units communicate through a bus called the ICC bus. The I/O unit senses an interrupt input, addresses it to a local unit, and sends it over the ICC bus. The local unit that is addressed accepts the message sent by the I/O unit.

In an MP-compliant system, one local APIC per CPU is required. Depending on the total number of interrupt lines in an MP system, one or more I/O APICs may be used. The bus interrupt line assignments can be implementation-specific and can be defined by the MP configuration table described in Chapter 4.

The Intel 82489DX APIC is a "discrete APIC" implementation. The programming interface of the 82489DX APIC units serves as the base of the MP specification. Each APIC has a version register that contains the version number of a specific APIC implementation. The version register of the 82489DX family has a version number of "0x," where *x* is a four-bit hexadecimal number. Version number "1x" refers to Pentium processors with integrated APICs, such as the Pentium 735\90 and 815\100 processors, and *x* is a four-bit hexadecimal number.

The integrated APIC maintains the same programming interface as the 82489DX APIC. Table 3-2 describes the features specific to the integrated APIC.

#### Table 3-2. APIC Versions

| АРІС Туре                                                   | Local APIC Version<br>Register (hexadecimal) | Integrated APIC Features                                                              |

|-------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------|

| 82489DX APIC                                                | 0x                                           |                                                                                       |

| Integrated APIC, i.e., Pentium processors (735\90, 815\100) | 1x                                           | STARTUP IPI. See Appendix B.4.2 for details.<br>Programmable interrupt input polarity |

#### NOTE:

*x* is a 4-bit hexadecimal number.

To encourage future extendibility and innovation, the Intel APIC architecture definition is limited to the programming interface of the APIC units. The ICC bus protocol and electrical specifications are considered implementation-specific. That is, while different versions of APIC implementations may execute the same binary software, different versions of APIC components may be implemented with different bus protocols or electrical specifications. Care must be taken when using different versions of the APIC in a system.

The APIC architecture is designed to be scaleable. The 82489DX APIC has an 8-bit ID register that can address from one to 255 APIC devices. Furthermore, the Logical Destination register for the 82489DX APIC supports 32 bits, which can address up to 32 devices. For small system implementations, the APIC ID register can be reduced to the least significant 4 bits and the Logical Destination register can be reduced to the most significant 8 bits.

To ensure software compatibility with all versions of APIC implementations, software developers must follow the following programming guidelines:

- 1. Assign an 8-bit APIC ID starting from zero.

- 2. Assign logical destinations starting from the most significant byte of the 32-bit register.

- 3. Program the APIC spurious vector to hexadecimal "xF," where x is a 4-bit hexadecimal number.

The following features are only available in the integrated APIC:

- 1. The I/O APIC interrupt input signal polarity can be programmable.

- 2. A new interprocessor interrupt, STARTUP IPI is defined.

In general, the operating system must use the STARTUP IPI to wake up application processors in systems with integrated APICs, but must use INIT IPI in systems with the 82489DX APIC. Refer to Appendix B, Section B.4, for application processor startup.

#### 3.6.2 Interrupt Modes

The MP specification defines three different interrupt modes as follows:

- 1. *PIC Mode*—effectively bypasses all APIC components and forces the system to operate in single-processor mode.

- 2. *Virtual Wire Mode*—uses an APIC as a virtual wire, but otherwise operates the same as PIC Mode.

- 3. Symmetric I/O Mode—enables the system to operate with more than one processor.

The first two interrupt modes, PIC Mode and Virtual Wire Mode, provide PC/AT-compatibility. At least one of these modes must be implemented in systems that comply with the MP specification. In these modes, full DOS compatibility with the uniprocessor PC/AT is provided by using the APICs in conjunction with standard 8259A-equivalent programmable interrupt controllers (PICs).

The third mode, Symmetric I/O Mode, must be implemented in addition to either PIC Mode or Virtual Wire Mode. An MP operating system is booted under either one of the two PC/AT-compatible modes. Later the operating system switches to Symmetric I/O Mode as it enters multiprocessor mode.

The interrupt modes are implemented by a combination of hardware and software. The hardware and programming specifications for each of these modes are further defined in the following subsections. BIOS programmers should refer to Appendix A, which includes information about programming the APIC for Virtual Wire Mode. Operating system programmers should refer to Appendix B, which provides more information about initializing the APIC for Symmetric I/O Mode.

#### 3.6.2.1 PIC Mode

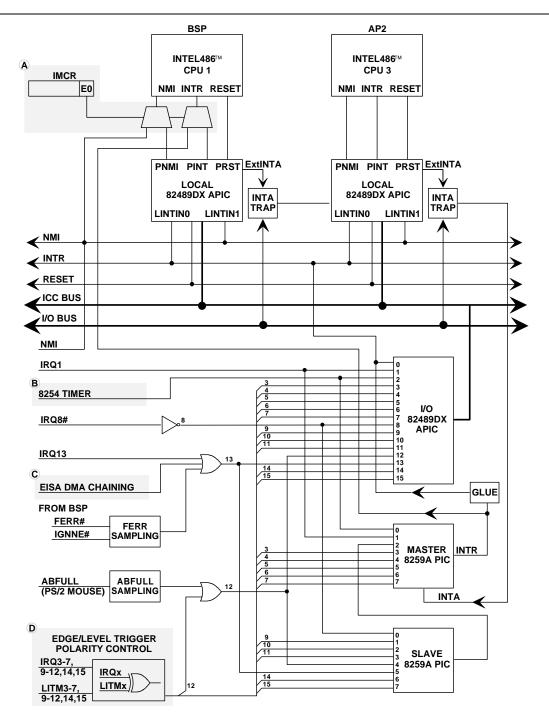

PIC Mode is software compatible with the PC/AT because it actually employs the same hardware interrupt configuration. As Figure 3-2 illustrates, the hardware for PIC Mode bypasses the APIC components by using an interrupt mode configuration register (IMCR). This register controls whether the interrupt signals that reach the BSP come from the master PIC or from the local APIC. Before entering Symmetric I/O Mode, either the BIOS or the operating system must switch out of PIC Mode by changing the IMCR.

Figure 3-2. PIC Mode

The IMCR is supported by two read/writable or write-only I/O ports, 22h and 23h, which receive address and data respectively. To access the IMCR, write a value of 70h to I/O port 22h, which selects the IMCR. Then write the data to I/O port 23h. The power-on default value is zero, which connects the NMI and 8259 INTR lines directly to the BSP. Writing a value of 01h forces the NMI and 8259 INTR signals to pass through the APIC.

The IMCR must be cleared after a system-wide INIT or RESET to enable the PIC Mode as default. (Refer to Section 3.7 for information on the INIT and RESET signals.)

The IMCR is optional if PIC Mode is not implemented. The IMCRP bit of the MP feature information bytes (refer to Chapter 4) enables the operating system to detect whether the IMCR is implemented.

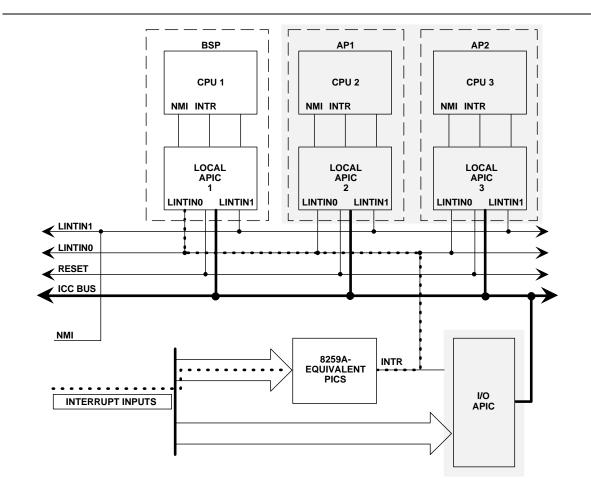

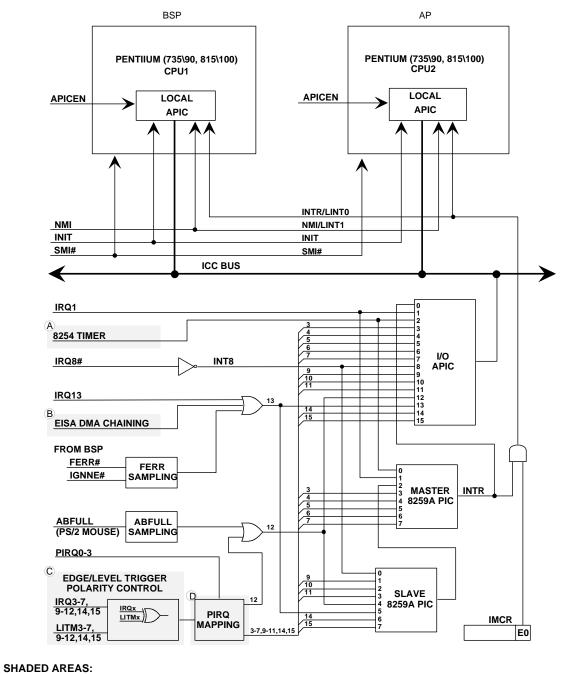

#### 3.6.2.2 Virtual Wire Mode

Virtual Wire Mode provides a uniprocessor hardware environment capable of booting and running all DOS shrink-wrapped software.

In Virtual Wire Mode, as shown in Figure 3-3, the 8259A-equivalent PIC fields all interrupts, and the local APIC of the BSP becomes a virtual wire, which delivers interrupts from the PIC to the BSP via the local APIC's local interrupt 0 (LINTIN0). The LINTIN0 pin of the local APIC is programmed as ExtINT, specifying to the APIC that the PIC is to serve as an external interrupt controller. Whenever the local APIC finds that a particular interrupt is of type ExtINT, it asserts the ExtINTA transaction along with the PINT interrupt to the processor. In this case, the I/O APIC is not used.

SHADED AREAS INDICATE UNUSED CIRCUITS. DOTTED LINE SHOWS INTERRUPT PATH.

Figure 3-3. Virtual Wire Mode via Local APIC

Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP's local APIC. It is also permissible to program the I/O APIC for Virtual Wire Mode, as shown in Figure 3-4. In this case the interrupt signal passes through both the I/O APIC and the BSP's local APIC.

SHADED AREAS INDICATE UNUSED CIRCUITS. DOTTED LINE SHOWS INTERRUPT PATH.

Figure 3-4. Virtual Wire Mode via I/O APIC

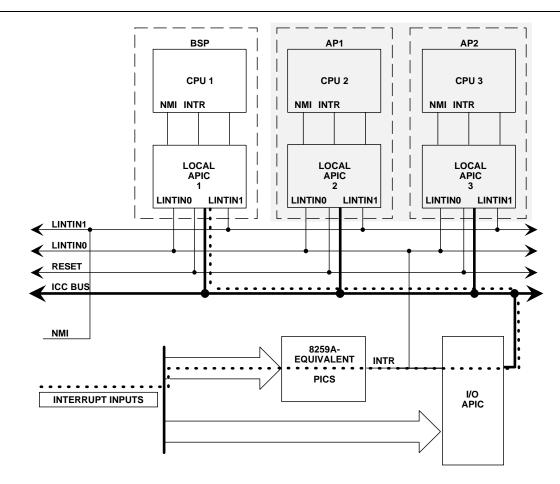

### 3.6.2.3 Symmetric I/O Mode

Some MP operating systems operate in Symmetric I/O Mode. This mode requires at least one I/O APIC to operate. In this mode, I/O interrupts are generated by the I/O APIC. All 8259 interrupt lines are either masked or work together with the I/O APIC in a mixed mode. See Figure 3-5 for an overview of Symmetric I/O Mode.

SHADED AREAS INDICATE UNUSED CIRCUITS. DOTTED LINE SHOWS INTERRUPT PATH.

#### Figure 3-5. Symmetric I/O Mode

The APIC I/O unit has general-purpose interrupt inputs that can be individually programmed to different operating modes. The I/O APIC interrupt line assignments are system implementation specific. Refer to Chapter 4 for custom implementations and to Chapter 5 for default configurations.

<u>The hardware must support a mode of operation in which the system can switch easily to</u> <u>Symmetric I/O mode from PIC or Virtual Wire mode. When the operating system is ready to</u> <u>switch to MP operation, it writes a 01H to the IMCR register, if that register is implemented, and</u> <u>enables I/O APIC Redirection Table entries. The hardware must not require any other action on the</u> <u>part of software to make the transition to Symmetric I/O mode.</u>

#### 3.6.3 Assignment of System Interrupts to the APIC Local Unit

The APIC local unit has two general-purpose interrupt inputs, which are reserved for system interrupts. These interrupt inputs can be individually programmed to different operating modes. Like the I/O APIC interrupt lines, the local APIC interrupt line assignments of a non-PC/AT-compatible system are system implementation specific. Refer to Chapter 4 for custom implementations and to Chapter 5 for default configurations.

#### 3.6.4 Floating Point Exception Interrupt

For PC/AT compatibility, the bootstrap processor must support DOS-compatible FPU execution and exception handling while running in either of the PC/AT-compatible modes. <u>This means that</u> floating point error signals from the BSP must be routed to the interrupt request 13 signal, IRQ13, when the system is in PIC or virtual wire mode. While floating point error signals from an application processor need not be routed to IRQ13, platform designers may choose to connect the two. For example, connecting the floating point error signal from application processors to IRQ13 can be useful in the case of a platform that supports dynamic choice of BSP during boot.

In <u>symmetric</u> mode, a compliant system supports only on-chip floating point units, with error signaling via interrupt vector 16. <u>Operating systems must use interrupt vector 16 to manage floating point exceptions when the system is in symmetric mode.</u>

It is recommended that hardware platforms be designed to block delivery of floating point exception signals from the processors once the system has switched into symmetric mode to avoid delivery of superfluous interrupts. If done, such blocking must be implemented in a manner that is transparent to the operating system. However, the operating system must still be prepared to handle interrupts generated through assertion of floating point error signals, because on some platforms these signals may still be routed to IRQ13 even after the switch to symmetric mode.

#### 3.6.5 APIC Memory Mapping

In a compliant system, all APICs must be implemented as memory-mapped I/O devices. APIC base addresses are at the top of the memory address space. All APIC local units are mapped to the same addresses, which are not shared. Each processor accesses its local APIC via these memory addresses. The default base address for the local APICs is 0FEE0\_0000h.

Unlike the local APICs, the I/O APICs are mapped to give shared access from all processors, providing full symmetric I/O access. The default base address for the first I/O APIC is 0FEC0\_0000h. Subsequent I/O APIC addresses are assigned in 4K increments. For example, the second I/O APIC is at 0FEC0\_1000h.

Non-default APIC base addresses can be used if the MP configuration table is provided. (Refer to Chapter 4.) However, the local APIC base address must be aligned on a 4K boundary, and the I/O APIC base address must be aligned on a 1K boundary.

### 3.6.6 APIC Identification

Systems developers must assign APIC local unit IDs and ensure that all are unique. There are two acceptable ways to assign local APIC IDs, as follows:

- By hardware. The ID of each APIC local unit is sampled from the appropriate pins at RESET.

- By the BIOS. Software can override the APIC IDs assigned by hardware by writing to the Local Unit ID Register. This is possible only with help from the hardware; for example, using board ID registers that the software can read to determine which board has the BSP.

Local APIC IDs must be <u>unique</u>, and need not be consecutive.

The MP operating system can use the local APIC ID to determine on which processor it is executing.

The ID of each I/O APIC unit is set to zero during RESET. It is the responsibility of the operating system to verify the uniqueness of the I/O APIC ID and to assign a unique ID if a conflict is found. The assignment of APIC IDs for I/O units must always begin from the lowest number that is possible after the assignment of local APIC IDs. The operating system must not attempt to change the ID of an APIC I/O unit if the preset ID number is acceptable.

#### 3.6.7 APIC Interval Timers

The 82489DX APIC local unit contains a 32-bit wide programmable timer with the following two independent clock input sources:

- 1. The CLK pin provides the clock signal that drives the 82489DX APIC's internal operation.

- 2. The TMBASE pin allows an independent clock signal to be connected to the 82489DX APIC for use by the timer functions.

The interval timers of the integrated APIC have only one clock input source, CLK. To maintain consistency, developers of compliant systems based on the 82489DX must choose CLK as the source of the 82489DX APIC timer clock. TMBASE must be left disabled. An MP operating system may use the IRQ8 real-time clock as a reference to determine the actual APIC timer clock speed.

Special consideration must be made for systems with stop clock (STPCLK#) capability. Timer interrupts are ignored while STPCLK# is asserted. The system time-of-day clock may need to be reset when STPCLK# is deasserted.

#### 3.6.8 Multiple I/O APIC Configurations

Systems may provide more than one I/O APIC for increased interrupt scalability in Symmetric I/O Mode. To preserve PC/AT compatibility in PIC or Virtual Wire mode, interrupts connected to additional I/O APICs must also be connected to the 8259A programmable interrupt controller. Figure 3-6 represents one possible interrupt connection scheme for a system with two I/O APICs.

The non-ISA interrupts are connected to both the 8259A IRQ inputs and the inputs of the associated I/O APIC. To prevent non-ISA interrupts from appearing at inputs on both I/O APICs, the hardware must provide a means to disable the interrupt routing network when the system switches to symmetric I/O mode with the second I/O APIC enabled.

More information about the implementation of multiple I/O APIC configurations is presented in Appendix D.

Figure 3-6. Multiple I/O APIC Configurations

#### 3.7 RESET Support

To bring all circuitry in a computer system to an initial state, computer systems require a systemwide reset capability. To support multiple processors, a compliant system requires a processorspecific reset or initialization capability in addition to the typical system-wide reset and initialization capabilities.

- The term "RESET" refers to the system-wide hard reset. It refers to the RESET signal on both Pentium and Intel486 processors or the RESET signal of the 82489DX APIC. (See Section 3.7.1.)

- The term "INIT," refers to either a system-wide soft reset/initialization or a processor-specific initialization. For example, the term "INIT" may refer to the INIT signal on the Pentium processor or to the RESET signal on the Intel486 processor. (See Sections 3.7.2. and 3.7.3.)

Because the INIT signal is available on the Pentium processor but not on the Intel486 processor, the remainder of this document uses the above-mentioned special definitions for the terms "INIT" and "RESET":

#### 3.7.1 System-wide RESET

The system-wide RESET, as defined by this specification, refers to a *hard* or *cold reset*, which sets all circuitry, including processor, coprocessor, add-in cards, and control logic, to an initial state. A hard reset is the reset signal that is sent to all components of the system during a power-on

or by the front panel reset button (if the system is so equipped). This type of reset operates without regard to cycle boundaries, and, for example, is connected to the RESET pin of Pentium processors.

#### 3.7.2 System-wide INIT

The system-wide INIT, as defined by this specification, refers to a *soft* or *warm reset* that initializes only portions of the processor. This type of reset initializes the microprocessor in such a way that the reset does not corrupt any pending cycles, but waits instead for a cycle boundary, and does not invalidate the contents of caches and floating point registers. This type of reset request is connected to the INIT signal of newer processors, such as the Pentium processors. On Intel486 processors, the RESET pin is used for this function, as well as for hard resets, but the RESET pin does not provide the advantages of the INIT pin. There are <u>many possible</u> ways to assert <u>a</u> soft reset, <u>including</u>:

- A write either to a port of the 8042 Keyboard Controller or to some other port provided for the same purpose by a chipset.

- A shutdown special bus cycle. Usually a chipset senses a shutdown cycle and asserts a soft reset to the processor.

In a compliant system, the standard PC/AT-platform resets mentioned above, both hard and soft, must be directed to all processors in the system, except in the case of fault-tolerant MP systems, in which a soft reset may be handled on a per-processor basis.

#### 3.7.3 Processor-specific INIT

A processor-specific INIT is one of the basic multiprocessor support functions of a compliant multiprocessor system, along with processor startup and shutdown. With it, the BSP can selectively initialize an AP for subsequent startup or recover an AP from a fatal system error. This type of INIT function is exclusively used by the MP operating system or BIOS self-test routine. The system must be designed so that the processor-specific INIT can be initiated by software programming; it is not necessary that it be initiated by hardware.

A compliant system supports the processor-specific INIT via a special interprocessor interrupt (IPI) mechanism called INIT IPI. For the 82489DX APIC, INIT IPI is an IPI that has the delivery mode RESET, which delivers the signal to all processors listed in the destination by asserting/deasserting the addressed APIC local unit's PRST output pin. When the PRST signal is connected to the INIT pin of the Pentium processor or to the RESET pin of the Intel486 processor, the INIT IPI forces the processor to begin executing at the reset vector.

For systems based on the Intel486 processor, the 82489DX APIC's PRST line must be the only line connected to the processor's RESET input, so that the INIT IPI resets the targeted processor only. The system reset signal is connected to the local 82489DX APIC's RESET input. Assertion of the system reset signal then causes all of the local 82489DX APICs to assert their PRST outputs, thereby resetting all the processors.

For integrated APIC versions of the Pentium processor, INIT IPI asserts and deasserts the internal INIT signal of the Pentium processor.

#### 3.8 System Initial State

The system initial state is the state before the BIOS gives control to the operating system. It is identical to the system initial state of a typical PC/AT system, with the additional MP components in the following state:

- 1. All local APICs are disabled, except for the local APIC of the BSP if the system starts in Virtual Wire Mode.

- 2. All pending I/O APIC interrupts are cleared and disabled.

- 3. If IMCR is present, it should be set to 0 or 1 depending on the interrupt mode chosen for startup.

- 4. All APs are in Real Mode.

- 5. All APs are in HALT state or off the system bus.

The BIOS must disable interrupts to all processors and set the APICs to the system initial state before giving control to the operating system. The operating system is responsible for initializing all of the APICs.

#### 3.9 Support for Fault-resilient Booting

OEMs may choose not to implement a fault-resilient booting capability in their systems. However, if such a capability is provided, systems developers must observe the following guidelines:

- BSP determination may be performed by special hardware or by the BIOS, but it must be totally transparent to the operating system.

- NMI and INTR must be connected to the BSP.

- FERR# and IGNNE# signals from the designated BSP must be used to support IRQ13.

- The A20M# signal from the designated BSP must be used to support the masking of physical address bit 20 on the BSP (to support DOS compatibility).

# 4 MP Configuration Table

The operating system must have access to some information about the multiprocessor configuration. The MP specification provides two methods for passing this information to the operating system: a minimal method for configurations that conform to one of a set of common hardware defaults, and a maximal method that provides the utmost flexibility in hardware design. Figure 4-1 shows the general layout of the MP configuration data structures.

Figure 4-1. MP Configuration Data Structures

The following two data structures are used:

- 1. The *MP Floating Pointer Structure*. This structure contains a physical address pointer to the MP configuration table and other MP feature information bytes. When present, this structure indicates that the system conforms to the MP specification. This structure must be stored in at least one of the following memory locations, because the operating system searches for the MP floating pointer structure in the order described below:

- a. In the first kilobyte of Extended BIOS Data Area (EBDA), or

- Within the last kilobyte of system base memory (e.g., 639K-640K for systems with 640 KB of base memory or 511K-512K for systems with 512 KB of base memory) if the EBDA segment is undefined, or

- c. In the BIOS ROM address space between 0F0000h and 0FFFFFh.

- 2. The MP Configuration Table. This table is optional. The table is composed of a base section and an extended section. The base section contains entries that are completely backwards compatible with previous versions of this specification. The extended section contains additional entry types. The MP configuration table contains explicit configuration information about APICs, processors, buses, and interrupts. The table consists of a header, followed by a number of entries of various types. The format and length of each entry depends on its type. When present, this configuration table must be stored either in a non-reported system RAM or within the BIOS read-only memory space.

An MP configuration table is not required if the system design corresponds to one of the default configurations listed in Chapter 5. Note that these defaults are only for designs that are always equipped with two processors. Systems that support a variable number of installed processors must supply a complete MP configuration table that indicates the correct number of installed processors. For example, systems that ship with only one processor but provide for a later upgrade with a second processor may not use a default MP configuration.

The following is a list of the suggested memory spaces for the MP configuration table:

- a. In the first kilobyte of Extended BIOS Data Area (EBDA), or

- b. Within the last kilobyte of system base memory if the EBDA segment is undefined, or

- c. At the top of system physical memory, or

- d. In the BIOS read-only memory space between 0E0000h and 0FFFFFh.

The BIOS reports the base memory size in a two-byte location (40:13h) of the BIOS data area. The base memory size is reported in kilobytes minus 1K, which is used by the EBDA segment or for other purposes.

The exact starting address of the EBDA segment for EISA or MCA systems can be found in a twobyte location (40:0Eh) of the BIOS data area. If system memory is used, the BIOS must not report this memory as part of the available memory space.

These two MP configuration data structures can be located in the ROM space only if the system is not dynamically reconfigurable. The MP configuration information is intended to be read-only to the operating system.

Strings in the configuration tables are coded in ASCII. The first character of the string is stored at the lowest address of the string field. If the string is shorter than its field, the extra character locations are filled with space characters. Strings are not null terminated.

# 4.1 MP Floating Pointer Structure

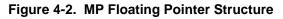

An MP-compliant system must implement the MP floating pointer structure, which is a variable length data structure in multiples of 16 bytes. Currently, only one 16-byte data structure is defined. It must span a minimum of 16 contiguous bytes, beginning on a 16-byte boundary, and it must be located within the physical address as specified in the previous section. To determine whether the system conforms to the MP specification, the operating system must search for the MP floating pointer structure in the order specified in the previous section. Figure 4-2 shows the format of this structure, and Table 4-1 explains each of the fields.

| Field                       | Offset<br>(in bytes:bits) | Length<br>(in bits) | Description                                                                                                                                                          |

|-----------------------------|---------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNATURE                   | 0                         | 32                  | The ASCII string represented by "_MP_" which<br>serves as a search key for locating the pointer<br>structure.                                                        |

| PHYSICAL ADDRESS<br>POINTER | 4                         | 32                  | The address of the beginning of the MP configuration table. All zeros if the MP configuration table does not exist.                                                  |

| LENGTH                      | 8                         | 8                   | The length of the floating pointer structure table<br>in paragraph (16-byte) units. The structure is 16<br>bytes or 1 paragraph long; so this field contains<br>01h. |

| SPEC_REV                    | 9                         | 8                   | The version number of the MP specification supported. <u>A value of 01h indicates Version 1.1.</u><br><u>A value of 04h indicates Version 1.4</u> .                  |

| CHECKSUM                    | 10                        | 8                   | A checksum of the complete pointer structure.<br>All bytes specified by the length field, including<br>CHECKSUM and reserved bytes, must add up to<br>zero.          |

#### Table 4-1. MP Floating Pointer Structure Fields

| Field                               | Offset<br>(in bytes:bits) | Length<br>(in bits) | Description                                                                                                                                                                                                                                               |

|-------------------------------------|---------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MP FEATURE<br>INFORMATION BYTE 1    | 11                        | 8                   | <b>Bits 0-7:</b> MP System Configuration Type.<br>When these bits are all zeros, the MP<br>configuration table is present. When nonzero,<br>the value indicates which default configuration<br>(as defined in Chapter 5) is implemented by the<br>system. |

| MP FEATURE                          | 12:0                      | 7                   | Bits 0-6: Reserved for future MP definitions.                                                                                                                                                                                                             |

| INFORMATION BYTE 2                  | 12:7                      | 1                   | <b>Bit 7:</b> IMCRP. When the IMCR presence bit is set, the IMCR is present and PIC Mode is implemented; otherwise, Virtual Wire Mode is implemented.                                                                                                     |

| MP FEATURE<br>INFORMATION BYTES 3-5 | 13                        | 24                  | Reserved for future MP definitions. Must be zero.                                                                                                                                                                                                         |

#### Table 4-1. MP Floating Pointer Structure Fields (continued)

The MP feature information byte 1 specifies the MP system default configuration type. If nonzero, the system configuration conforms to one of the default configurations. The default configurations, specified in Chapter 5, <u>may only be used to describe systems that always have two processors installed.</u>

Bit 7 of MP feature information byte 2, the IMCR present bit, is used by the operating system to determine whether PIC Mode or Virtual Wire Mode is implemented by the system.

The physical address pointer field contains the address of the beginning of the MP configuration table. If it is nonzero, the MP configuration table can be accessed at the physical address provided in the pointer structure. This field must be all zeros if the MP configuration table does not exist.

# 4.2 MP Configuration Table Header

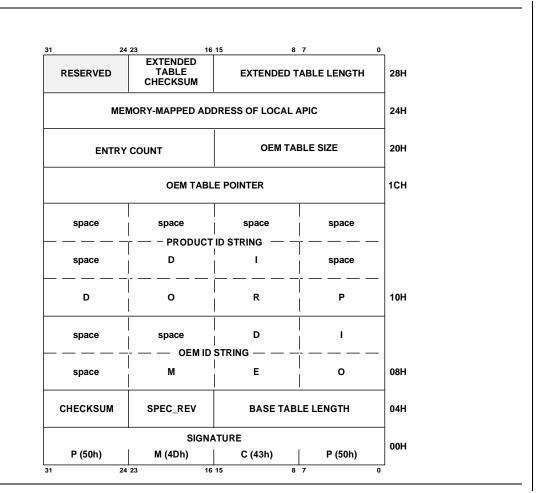

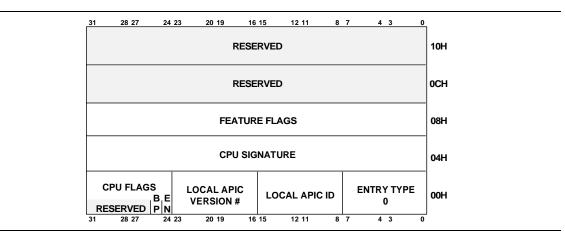

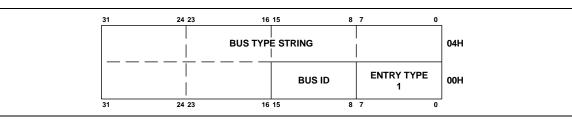

Figure 4-3 shows the format of the header of the MP configuration table, and Table 4-2 explains each of the fields.

Figure 4-3. MP Configuration Table Header

| Field                      | Offset<br>(in bytes) | Length<br>(in bits) | Description                                                                                                                                                                                            |

|----------------------------|----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNATURE                  | 0                    | 32                  | The ASCII string representation of "PCMP," which confirms the presence of the table.                                                                                                                   |

| BASE TABLE LENGTH          | 4                    | 16                  | The length of the <u>base</u> configuration table in bytes,<br><u>including the header,</u> starting from offset 0. This field<br>aids in calculation of the checksum.                                 |

| SPEC_REV                   | 6                    | 8                   | The version number of the MP specification. <u>A value</u><br>of 01h indicates Version 1.1. A value of 04h indicates<br>Version 1.4.                                                                   |

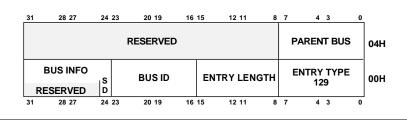

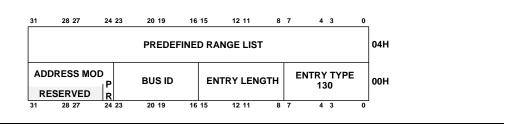

| CHECKSUM                   | 7                    | 8                   | A checksum of the entire <u>base</u> configuration table. All bytes, including CHECKSUM and reserved bytes, must add up to zero.                                                                       |