# Audio Codec '97

# **Component Specification**

Revision 1.03 September 15, 1996

Primary developers:

Analog Devices Creative Labs Intel Corporation National Semiconductor Yamaha Corporation

### **REVISION HISTORY**

| <ul> <li>AC '97 Component Specification revision 1.0, released May 17, 1996</li> <li>Page 32, 6.3: duplicate 6.3 heading moved and renamed 6.1.1 (no text changed)<br/>Page 34, 6.3.1, para 2, line 3: the each vendors<br/>Page 39, 6.3.11, para 1, line 4: this bits 0-7.</li> <li>AC '97 Component Specification revision 1.02, posted on the Web June 1, 1996<br/>Cover changed (no content changed)</li> <li>AC '97 Component Specification revision 1.03, updated September 22, 1996</li> <li>Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package</li> <li>Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard</li> <li>Page 11, 2., Packaging, para 3: The standard attractive a requirement for migrating baseline motherboard</li> <li>Page 18, 3.3, Table 5, 1st entry: Vref Vref4</li> <li>Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28</li> <li>Page 29, 5.2, para 1:When AC '97's General Purpece Register (20h); Powerdown Register (26h), is</li> <li>Page 33, 6.3, Table 7: PC BEEP Default x000h can be 0000h or 8000h (mute off or on)</li> <li>Page 33, 6.3, Table 7: PC DEEP Default x000h can be 0000h or 8000h. (mute off or on)</li> <li>Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.</li> <li>Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.</li> <li>Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)</li> <li>Page 43, 9.1, para 1:by the General Purpece Register (index 20h) Powerdown Register (26h).</li> <li>Page 43, 9.1, para 1:by the General Purpece Register (index 20h) Powerdown Register (26h).</li> <li>Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to</li> <li>Page 36, 6.3.4, PC Beep, para 4: Insert</li></ul> |      |                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| Page 34, 6.3.1, para 2, line 3: the each vendors         Page 39, 6.3.11, para 1, line 4: bits bits 0-7.         1.02       AC '97 Component Specification revision 1.02, posted on the Web June 1, 1996         Cover changed (no content changed)         1.03       AC '97 Component Specification revision 1.03, updated September 22, 1996         Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package         Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard         Page 13, 2., Packaging, para 3: The standard alternate 64-pin package         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h), Powerdown Register (26h), is         Page 33, 6.3, Table 7: Po. BEEP Default x000 can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 43, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 43, 6.3.9, apt control Register: linear or logarithmic implementation is acceptable (linear is s                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.00 | AC '97 Component Specification revision 1.0, released May 17, 1996                                                      |

| Page 39, 6.3.11, para 1, line 4: bits bits 0-7.         1.02       AC '97 Component Specification revision 1.02, posted on the Web June 1, 1996         Cover changed (no content changed)         1.03       AC '97 Component Specification revision 1.03, updated September 22, 1996         Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package         Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard         Page 11, 2., Packaging, para 3: The standard alternate 64-pin package         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 3: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (adex 20h) Powerdown Register (26h).         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.01 |                                                                                                                         |

| <ul> <li>AC '97 Component Specification revision 1.02, posted on the Web June 1, 1996</li> <li>Cover changed (no content changed)</li> <li>AC '97 Component Specification revision 1.03, updated September 22, 1996</li> <li>Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package</li> <li>Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard</li> <li>Page 15, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs</li> <li>Page 18, 3.3, Table 5, 1st entry: Vref Vref4</li> <li>Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28</li> <li>Page 19, 3.3, bullets: added references to CAP25-CAP28</li> <li>Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is</li> <li>Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h) Powerdown Register (26h), is</li> <li>Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h), with PR4.</li> <li>Page 33, 6.3, Table 7: PC_EEP Default x000h can be 0000h or 8000h (mute off or on)</li> <li>Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.</li> <li>Page 38, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on</li> <li>Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)</li> <li>Page 41, 7., para 1:by the General Purpose Register (now 20h) Register (26h).</li> <li>Page 43, 9.1., para 1:by the General Purpose Register (now 20h) Powerdown Register (26h).</li> <li>Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on</li> <li>Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)</li> <li>Page 41</li></ul>                             |      | Page 34, 6.3.1, para 2, line 3: the each vendors                                                                        |

| Cover changed (no content changed)         1.03       AC '97 Component Specification revision 1.03, updated September 22, 1996         Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package         Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard         Page 11, 2., Packaging, para 3: The standard alternate 64-pin package         Page 18, 3.3, Table 5, 1st entry: Vref Vref4         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h), Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 38, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.4, PC Beep, para 3: Note: The PC Beeep is recommended required to be routed to<                                                                                                                                                                                                                                                                                                                                                                                                                         |      | Page 39, 6.3.11, para 1, line 4: bits 0-7.                                                                              |

| <ul> <li>AC '97 Component Specification revision 1.03, updated September 22, 1996</li> <li>Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package</li> <li>Page 11, 2., Packaging, para 2:48-pin package is attractive e-requirement for migrating baseline motherboard</li> <li>Page 11, 2., Packaging, para 3: The standard alternate 64-pin package</li> <li>Page 13, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs</li> <li>Page 18, 3.3, Table 5: atded references to CAP2, CAP11-CAP13, CAP25-CAP28</li> <li>Page 19, 3.3, bullets: added references to CAP2-CAP23</li> <li>Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is</li> <li>Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), with PR4.</li> <li>Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h), with PR4.</li> <li>Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)</li> <li>Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.</li> <li>Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on</li> <li>Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)</li> <li>Page 41, 7., para 1:by the General Purpose Register (adhx -20h) Powerdown Register (26h).</li> <li>Page 43, 9.1., parenthesis: (T<sub>amblent</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V <i>H</i> 5%;</li> <li>Page 43, 9.1., para 2:writes to the General Purpose Powerdown Register are performed</li> <li>Page 43, 9.1., pare 1: added for spece for Max rise and fall times (or all entries in table)</li> <li>Page 48, 10., parenthesis: T<sub>amblent</sub> = 25°C, AVdd = DVdd = 5.0 V <i>H</i> 5%; tone and 3D disabled).</li> </ul>                 | 1.02 | AC '97 Component Specification revision 1.02, posted on the Web June 1, 1996                                            |

| Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package         Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard         Page 11, 2., Packaging, para 3: The standard alternate 64-pin package         Page 15, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, 30 Dorntol Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Registe                                                                                                                                                                                                                                                                                                                                                                                         |      | Cover changed (no content changed)                                                                                      |

| Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard         Page 11, 2., Packaging, para 3: The standard atternate 64-pin package         Page 15, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs         Page 18, 3.3, Table 5: 1st entry: Vref 4         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP2. CAP11-CAP13, CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (adex 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V or 3.3V t+' 5%;         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V or 3.3V t+' 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation                                                                                                                                                                                                                                                                                                                                                                         | 1.03 | AC '97 Component Specification revision 1.03, updated September 22, 1996                                                |

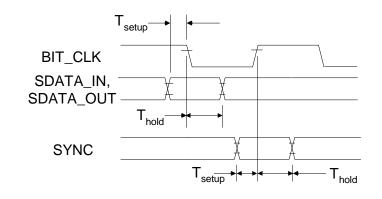

| Page 11, 2, Packaging, para 3: The standard alternate 64-pin package         Page 15, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs         Page 18, 3.3, Table 5, 1st entry: Vref Vref4         Page 18, 3.3, Table 5, 1st entry: Vref Vref4         Page 19, 3.3, bullets: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h), Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were <u>GN5</u> , now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>amblent</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table:                                                                                                                                                                                                                                                                                                                                                                                        |      | Page 7, 1.1, Feature List, bullet 2: Two standard packages: 48-pins package, alternate and 64-pins package              |

| Page 15, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs         Page 18, 3.3, Table 5, 1st entry: Vref Vref4         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 41, 7., para 2:writes to the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)                                                                                                                                                                                                                                                                                                                                                                                             |      | Page 11, 2., Packaging, para 2:48-pin package is attractive a requirement for migrating baseline motherboard            |

| Page 18, 3.3, Table 5, 1st entry: Vref Vref1         Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h), with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were <u>GN5</u> , now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7, para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., para 1:by the General Purpose Powerdown Register are performed         Page 43, 9.1., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., para 2: ad                                                                                                                                                                                                                                                                                                                                                                                                                     |      | Page 11, 2., Packaging, para 3: The standard alternate 64-pin package                                                   |

| Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28         Page 19, 3.3, bullets: added references to CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h), Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were <u>GN5</u> , now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 38, 6.3.9, D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 43, 9.1., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold t                                                                                                                                                                                                                                                                                                                                                |      | Page 15, 2.2, Table 2: 64-pin package "Reserved" pins 41-44 assigned as generic caps or multi-channel outputs           |

| Page 19, 3.3, bullets: added references to CAP25-CAP28         Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h), Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V or 3.3V 4/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V 4/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | Page 18, 3.3, Table 5, 1st entry: Vref Vref1                                                                            |

| Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is         Page 29, 5.2, para 2:the write to the General Purpose Register (20h), Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were GN5, now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | Page 18, 3.3, Table 5: added references to CAP2, CAP11-CAP13, CAP25-CAP28                                               |

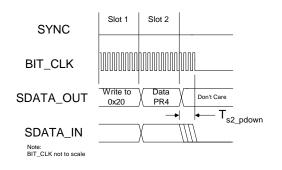

| Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h) with PR4.         Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were <u>GN5</u> , now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      | Page 19, 3.3, bullets: added references to CAP25-CAP28                                                                  |

| Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)         Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were <u>GN5</u> , now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., notte: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | Page 29, 5.2, para 1:When AC '97's General Purpose Register (20h), Powerdown Register (26h), is                         |

| Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were <u>GN5</u> , now X (don't care)         Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the <u>General Purpose Register (index 20h)</u> Powerdown Register (26h).         Page 43, 9.1., para 2:writes to the <u>General Purpose Powerdown Register are performed</u> Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | Page 29, 5.2, para 2:the write to the General Purpose Register (20h) Powerdown Register (26h) with PR4.                 |

| Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      | Page 33, 6.3, Table 7: PC_BEEP Default x000h can be 0000h or 8000h (mute off or on)                                     |

| Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to         Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 43, 9.1., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      | Page 33, 6.3, Table 7: Phone Volume (0Ch) and Mic Volume (0Eh) register D5 bits: were GN5, now X (don't care)           |

| Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on         Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 41, 7., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>amblent</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>amblent</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | Page 36, 6.3.4, PC Beep, para 2: Inserted new 2nd paragraph and reference to AC '97 FAQ for further details.            |

| Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)         Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 41, 7., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | Page 36, 6.3.4, PC Beep, para 3: Note: The PC Beep is recommended required to be routed to                              |

| Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).         Page 41, 7., para 2:writes to the General Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25°C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | Page 36, 6.3.4, PC Beep, para 4: The default value can be 0000h or 8000hmute off or on                                  |

| Page 41, 7., para 2:writes to the Ceneral Purpose Powerdown Register are performed         Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>0</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | Page 38, 6.3.9, 3D Control Register: linear or logarithmic implementation is acceptable (linear is shown)               |

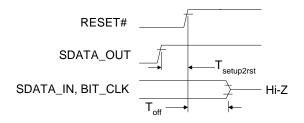

| Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;         Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | Page 41, 7., para 1:by the General Purpose Register (index 20h) Powerdown Register (26h).                               |

| Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),         Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | Page 41, 7., para 2:writes to the General Purpose Powerdown Register are performed                                      |

| Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation         Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | Page 43, 9.1., parenthesis: (T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V or 3.3V +/- 5%;              |

| Page 46, 9.2.3., figure: shows setup and hold times for SYNC, SDATA_OUT, and SDATA_IN (at Controller)         Page 46, 9.2.4., table: added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | Page 43, 9.1., NOTE: either 5.0V or 3.3V (+/- 5%),                                                                      |

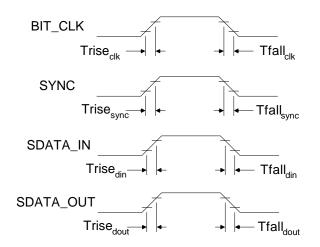

| Page 46, 9.2.4., table:       added 6nS spec for Max rise and fall times (for all entries in table)         Page 48, 10., parenthesis: $T_{ambient} = 25^{\circ}C$ , AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | Page 43, 9.1., para 2: added 2nd paragraph and 2 tables specifying PCI 2.1 compliant 5.0 V and 3.3 V operation          |

| <b>Page 48, 10., parenthesis:</b> $T_{ambient} = 25^{\circ}C$ , AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                                                                                                         |

| <b>Bage 48 10 Table:</b> Vrefout specid at 2.25 - 2.75 V typical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | Page 48, 10., parenthesis: T <sub>ambient</sub> = 25 <sup>o</sup> C, AVdd = DVdd = 5.0 V +/- 5%; tone and 3D disabled). |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | Page 48, 10., Table: Vrefout spec'd at 2.25 - 2.75 V typical                                                            |

| Page 48, 10., Note 7: added clarification of Stop Band rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | Page 48, 10., Note 7: added clarification of Stop Band rejection                                                        |

| Page 48, 10., Note 8: added clarification of Out-of-Band rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | Page 48, 10., Note 8: added clarification of Out-of-Band rejection                                                      |

Please send comments on this document to:

Audio Codec '97 Working Group:

audio97@intel.com

### NOTICES

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

INTEL DISCLAIMS ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. INTEL DOES NOT WARRANT OR REPRESENT THAT SUCH IMPLEMENTATION(S) WILL NOT INFRINGE SUCH RIGHTS.

#### LICENSING

A license is hereby granted to copy and reproduce this specification for internal use only. No other license, express or implied, by estoppel or otherwise, to any other intellectual property rights is granted herein.

A royalty-free, limited license is available to anyone who wishes to make use of this Audio Codec '97 specification. Please contact Intel at audio97@intel.com or the address below for specific Audio Codec '97 licensing terms.

Intel Corporation 2200 Mission College Blvd Santa Clara, CA 95052

Attention: Vincent Fung, M/S SC9-59

\* Designated product and corporate names may be trademarks of other companies and are used only for explanation and to the owners' benefit, without intent to infringe.

Copyright **ã** 1996, Intel Corporation. All Rights Reserved.

### **TABLE OF CONTENTS**

| 1. INTRODUCTION                                                                                                                 | 7    |

|---------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1. Feature List                                                                                                               | 7    |

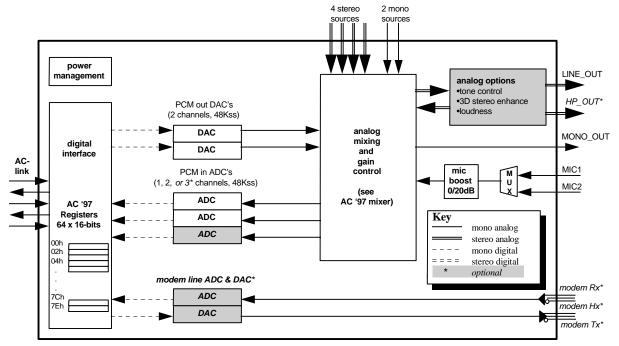

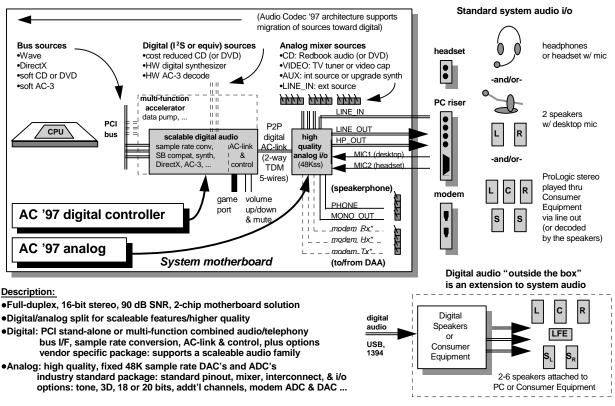

| 1.2. AUDIO CODEC '97 ARCHITECTURAL OVERVIEW                                                                                     |      |

| 1.3. INTEGRATING AC '97 INTO THE SYSTEM                                                                                         |      |

| 1.4. Software Driver Support and AC '97 Controller / AC '97 Interoperability                                                    | 10   |

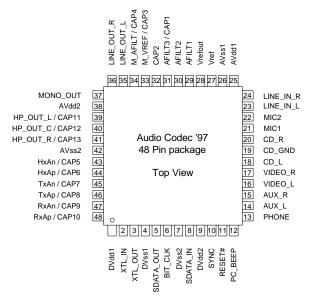

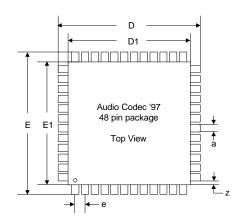

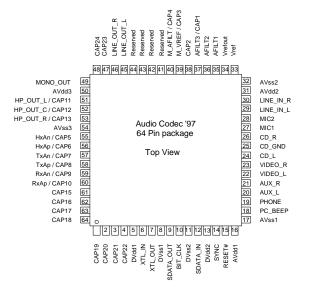

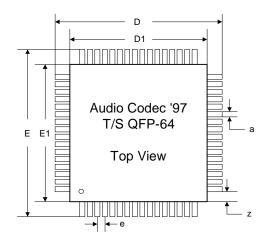

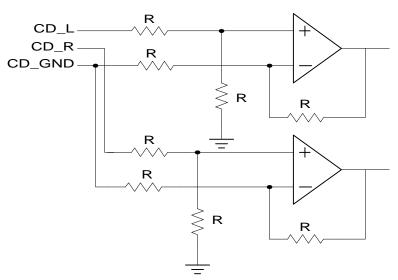

| 2. PACKAGING                                                                                                                    | 11   |

| 2.1 48-pin QFP package                                                                                                          | . 12 |

| 2.2 64-pin QFP package                                                                                                          |      |

| 3. PIN/SIGNAL DESCRIPTIONS                                                                                                      | . 16 |

| 3.1. DIGITAL I/O                                                                                                                | 16   |

| 3.2. ANALOG I/O                                                                                                                 |      |

| 3.3. FILTER/REFERENCES                                                                                                          |      |

| 3.4. Power and Ground Signals                                                                                                   | . 19 |

| 4. SYSTEM USAGE                                                                                                                 | 21   |

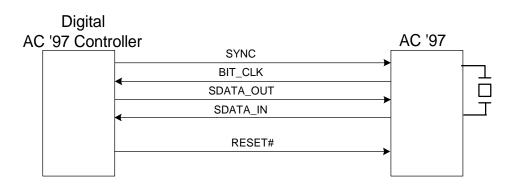

| 4.1. AC '97 CONNECTION TO THE DIGITAL AC '97 CONTROLLER                                                                         | 21   |

| 4.2. Clocking                                                                                                                   |      |

| 4.3. Resetting AC '97                                                                                                           | 22   |

| 5. DIGITAL INTERFACE                                                                                                            | . 23 |

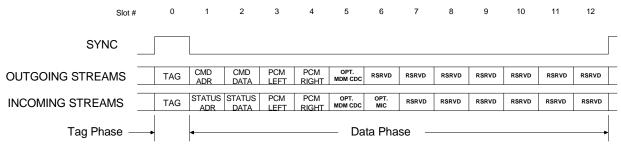

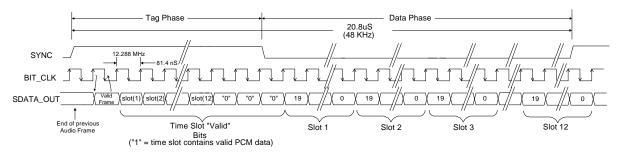

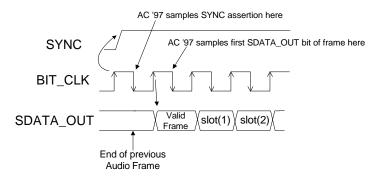

| 5.1. AC-LINK DIGITAL SERIAL INTERFACE PROTOCOL                                                                                  | 23   |

| 5.1.1. AC-link Audio Output Frame (SDATA_OUT)                                                                                   | -    |

| 5.1.1.1. Slot 1: Command Address Port                                                                                           |      |

| 5.1.1.2. Slot 2: Command Data Port                                                                                              |      |

| 5.1.1.3. Slot 3: PCM Playback Left Channel                                                                                      |      |

| <ul><li>5.1.1.4. Slot 4: PCM Playback Right Channel.</li><li>5.1.1.5. Slot 5: Optional Modem Line Codec</li></ul>               |      |

| 5.1.1.6. Slots 6-12: Reserved                                                                                                   |      |

| 5.1.2. AC-link Audio Input Frame (SDATA_IN)                                                                                     |      |

| 5.1.2.1. Slot 1: Status Address Port                                                                                            |      |

| 5.1.2.2. Slot 2: Status Data Port                                                                                               |      |

| 5.1.2.3. Slot 3: PCM Record Left Channel                                                                                        |      |

| 5.1.2.4. Slot 4: PCM Record Right Channel                                                                                       |      |

| <ul><li>5.1.2.5. Slot 5: Optional Modem Line Codec</li><li>5.1.2.6. Slot 6: Optional Dedicated Microphone Record Data</li></ul> |      |

| 5.1.2.7. Slots 7-12: Reserved                                                                                                   |      |